# Power Architecture® 32-bit Application Binary Interface Supplement 1.0 -Linux®

Ryan S. Arnold IBM

**Greg Davis Green Hills**

Brian Deitrich Freescale Semiconductor

Michael Eager Eager Consulting

Emil Medve Freescale Semiconductor

Steven J. Munroe IBM

Joseph S. Myers CodeSourcery

Steve Papacharalambous Freescale Semiconductor

Anmol P. Paralkar Freescale Semiconductor

Katherine Stewart Freescale Semiconductor

Edmar Wienskoski Freescale Semiconductor

### Power Architecture® 32-bit Application Binary Interface Supplement 1.0 - Linux®

by Ryan S. Arnold, Greg Davis, Brian Deitrich, Michael Eager, Emil Medve, Steven J. Munroe, Joseph S. Myers, Steve Papacharalambous, Anmol P. Paralkar, Katherine Stewart, and Edmar Wienskoski

1.0 Edition

Published April 19, 2011

Copyright © 1999, 2003, 2004 IBM Corporation

Copyright © 2002 Freescale Semiconductor, Inc.

Copyright © 2003, 2004 Free Standards Group

Copyright © 2011 Power.org

The ATR-LINUX portions of this document are derived from the 64-bit PowerPC ELF Application Binary Interface Supplement 1.8, originally written by Ian Lance Taylor under contract for IBM, with later revisions by: David Edelsohn, Torbjorn Granlund, Mark Mendell, Kristin Thomas, Alan Modra, Steve Munroe, and Chris Lorenze.

The ATR-TLS and ATR-SECURE-PLT sections of this document are original contributions of IBM written by Alan Modra and Steven Munroe.

The ATR-SPE and ATR-EABI portions of this document are derived from material used to write the E500 ABI and are contributed by Freescale Semiconductor.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.3; with no Invariant Sections, with no Front-Cover Texts, and with no Back-Cover Texts. A copy of the license is available from <a href="http://www.gnu.org/licenses/fdl-1.3.txt">http://www.gnu.org/licenses/fdl-1.3.txt</a>.

The following terms are trademarks or registered trademarks of International Business Machines Corporation in the United States and/or other countries: AIX®, PowerPC®, VMX®, POWER<sup>TM</sup>. A full list of U.S. trademarks owned by IBM may be found at http://www.ibm.com/legal/copytrade.shtml.

The following terms are trademarks or registered trademarks of Freescale Semiconductor in the United States and/or other countries: AltiVec<sup>TM</sup>, e500<sup>TM</sup>. Information on the list of U.S. trademarks owned by Freescale Semiconductor may be found at http://www.freescale.com/files/abstract/help\_page/TERMSOFUSE.html.

The following terms are trademarks or registered trademarks of Power.org in the United States and/or other countries: Power ISA<sup>TM</sup>, Power Architecture®. Information on the list of U.S. trademarks owned by Power.org may be found at http://www.power.org/brand\_center/home/.

Linux® is the registered trademark of Linus Torvalds in the U.S. and other countries. Further information on this trademark can be found at http://www.linuxfoundation.org/programs/legal/trademark.

Revision History

Revision 1.0 April 19, 2011 Revised by: Power.org PowerABI TSC

# **Table of Contents**

| Preface                                                   | ix |

|-----------------------------------------------------------|----|

| 1. How To Read This Document                              | ix |

| 2. Section Numbering                                      | X  |

| 1. Introduction                                           | 1  |

| 1.1. Reference Documentation                              | 1  |

| 2. Software Installation                                  |    |

| 2.1. Physical Distribution Media and Formats              |    |

| 3. Low Level System Information                           |    |

|                                                           |    |

| 3.1. Machine Interface                                    |    |

| 3.1.1. Processor Architecture                             |    |

| 3.1.2.1 Pt 4.0.0 Initial                                  |    |

| 3.1.2.1. Byte Ordering                                    |    |

| 3.1.2.2. Fundamental Types                                |    |

| 3.1.2.3. Aggregates and Unions                            |    |

|                                                           |    |

| 3.2. Function Calling Sequence                            |    |

| 3.2.1.1. Register Roles                                   |    |

| 3.2.1.2. Limited-Access Bits                              |    |

| 3.2.2. The Stack Frame                                    |    |

| 3.2.2.1. General Stack Frame Requirements                 |    |

| 3.2.2.2. Optional Save Areas                              |    |

| 3.2.3. Parameter Passing                                  |    |

| 3.2.3.1. Parameter Passing Register Selection Algorithm   |    |

| 3.2.3.2. Parameter Passing Examples                       |    |

| 3.2.4. Variable Argument Lists                            |    |

| 3.2.5. Return Values.                                     |    |

| 3.3. Coding Examples                                      |    |

| 3.3.2. Code Model Overview                                |    |

| 3.3.3. Function Prologue and Epilogue                     |    |

| 3.3.3.1. The Purpose of a Function's Prologue             |    |

| 3.3.3.2. The Purpose of a Function's Epilogue             |    |

| 3.3.3.3. Rules for Prologue and Epilogue Sequences        |    |

| 3.3.4. Register Saving and Restoring Functions            |    |

| 3.3.4.1. Details about the Functions                      |    |

| 3.3.4.2. Register Saving and Restoring Functions (Vector) |    |

| 3.3.5. Profiling                                          |    |

| 3.3.6. Data Objects                                       |    |

| 3.3.7. Function Calls                                     |    |

| 3.3.8. Branching                                          |    |

| 3.3.9. Dynamic Stack Space Allocation                     |    |

| 3.4. DWARF Definition                                     | 72 |

| 3.5. Exception Handling                                   | 73 |

| 4. Object Files                                       | 74  |

|-------------------------------------------------------|-----|

| 4.3. ELF Header                                       | 74  |

| 4.4. Special Sections                                 |     |

| 4.6. Symbol Table                                     |     |

| 4.6.1. Symbol Values                                  |     |

| 4.7. Small Data Area                                  |     |

| 4.7.1. Use of the Small Data Area in Executables      | 78  |

| 4.7.2. Use of the Small Data Area in Shared Objects   | 78  |

| 4.9. DWARF Additions                                  | 79  |

| 4.10. APU Information Section                         | 79  |

| 4.13. Relocation Types                                | 81  |

| 4.13.1. Relocation Fields                             | 82  |

| 4.13.2. SPE Specific Relocation Fields                | 83  |

| 4.13.4. Relocation Notations                          | 84  |

| 4.13.5. Relocation Types Table                        | 85  |

| 4.13.6. Relocation Descriptions                       | 89  |

| 4.15. Thread Local Storage ABI                        | 91  |

| 4.15.1. TLS Background                                | 92  |

| 4.15.2. TLS Runtime Handling                          | 92  |

| 4.15.3. TLS Access Models                             | 94  |

| 4.15.3.1. General Dynamic TLS Model                   | 94  |

| 4.15.3.2. Local Dynamic TLS Model                     | 94  |

| 4.15.3.3. Initial Exec TLS Model                      |     |

| 4.15.3.4. Local Exec TLS Model                        | 96  |

| 4.15.4. TLS Link Editor Optimizations                 |     |

| 4.15.4.1. General Dynamic to Initial Exec             |     |

| 4.15.4.2. General Dynamic to Local Exec               |     |

| 4.15.4.3. Local Dynamic to Local Exec                 |     |

| 4.15.4.4. Initial Exec to Local Exec                  |     |

| 4.15.5. ELF TLS Definitions                           | 100 |

| 5. Program Loading and Dynamic Linking                | 105 |

| 5.1. Program Loading                                  | 105 |

| 5.1.1. Addressing Models                              | 108 |

| 5.2. Dynamic Linking                                  | 108 |

| 5.2.1. Program Interpreter                            | 108 |

| 5.2.2. Dynamic Section                                | 108 |

| 5.2.3. Global Offset Table                            | 109 |

| 5.2.3.1. Global Offset Table Under The Secure-PLT ABI | 109 |

| 5.2.3.2. Global Offset Table Under The BSS-PLT ABI    | 110 |

| 5.2.4. Function Addresses                             | 111 |

| 5.2.5. Procedure Linkage Table                        | 112 |

| 5.2.5.1. BSS Procedure Linkage Table                  | 112 |

| 5.2.5.2. Secure Procedure Linkage Table               | 116 |

| 6. Libraries                                                  | 120 |

|---------------------------------------------------------------|-----|

| 6.1. Library Requirements                                     | 120 |

| 6.1.1. C Library Conformance with Generic ABI                 | 120 |

| 6.1.1.1. Malloc Routine Return Pointer Alignment              | 120 |

| 6.1.1.2. Library Handling of Limited-access Bits in Registers | 120 |

| 6.1.2. Save and Restore Routines                              | 120 |

| 6.1.2.1. Save and Restore Routine Suffixes                    | 120 |

| 6.1.2.2. Save and Restore Routine Templates                   | 122 |

| 6.1.3. Types Defined In Standard Header                       | 124 |

| A. Taxonomy                                                   | 127 |

| B. Attribute Inclusion and ABI Conformance                    | 131 |

| B.1. ATR-LINUX Inclusion and Conformance                      | 131 |

| B.2. ATR-EABI Inclusion and Conformance                       | 132 |

| C. APUs and Power ISA Categories                              | 134 |

# **List of Figures**

| 3-1. Structure Smaller Than a Word                                         | 11  |

|----------------------------------------------------------------------------|-----|

| 3-2. Structure With No Padding                                             | 12  |

| 3-3. Structure With Internal Padding                                       | 12  |

| 3-4. Structure With Internal and Tail Padding                              | 13  |

| 3-5. Union Allocation                                                      | 13  |

| 3-6. Simple Bit-field Allocation                                           | 15  |

| 3-7. Bit-Field Allocation With Boundary Alignment                          | 16  |

| 3-8. Bit-Field Allocation With Storage Unit Sharing                        | 17  |

| 3-9. Bit-Field Allocation In A Union                                       |     |

| 3-10. Bit-Field Allocation With Unnamed Bit-Fields                         | 18  |

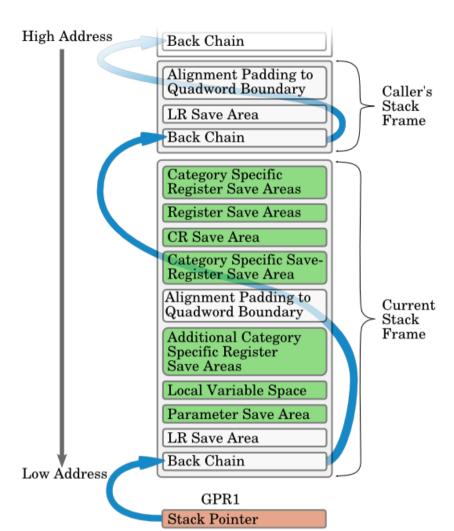

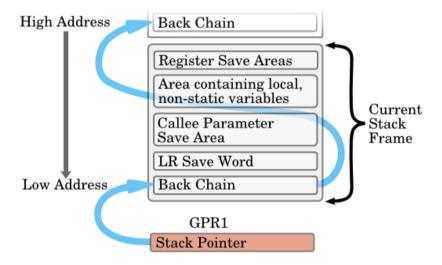

| 3-11. Stack Frame Organization                                             |     |

| 3-12. Example Minimum Stack Frame Allocation                               | 31  |

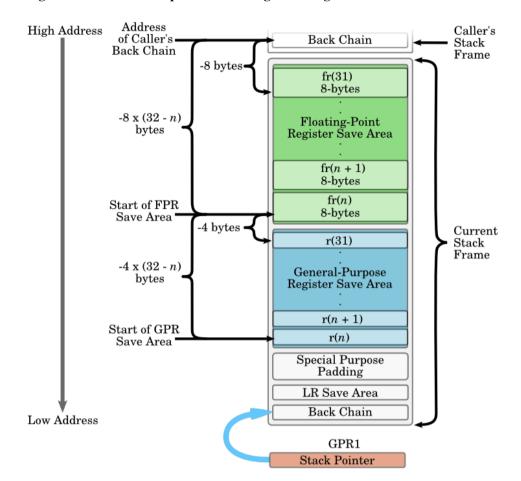

| 3-13. General-Purpose and Floating-Point Register Save Areas               | 31  |

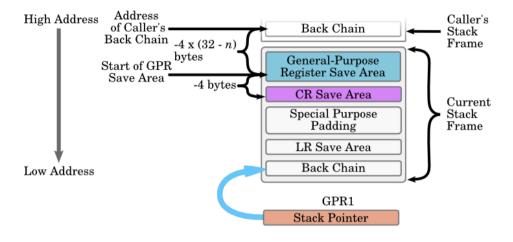

| 3-15. CR Save Area                                                         | 33  |

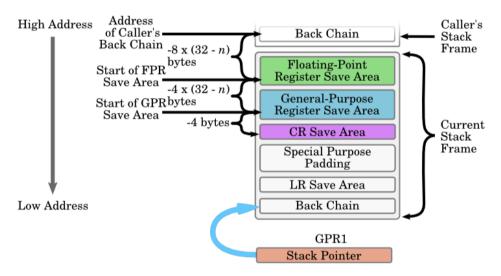

| 3-16. CR Save Area With Floating-Point Save Area                           | 33  |

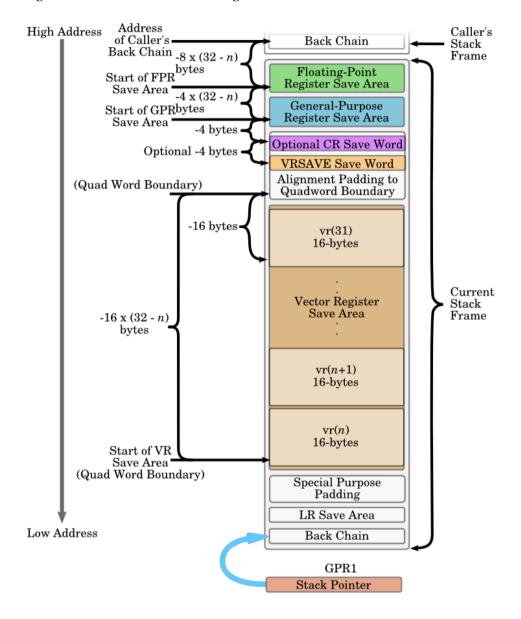

| 3-17. VRSAVE and Vector Register Save Areas                                | 34  |

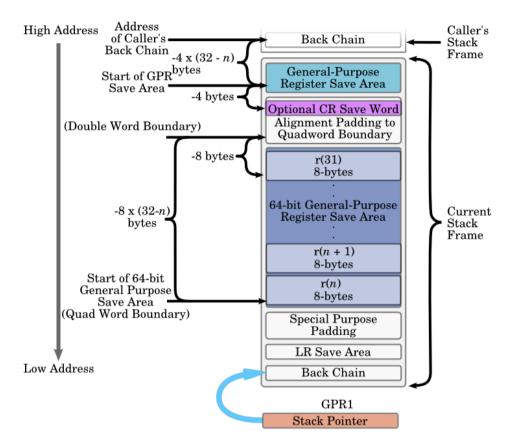

| 3-18. SPE 64-bit General-Purpose Register Save Area                        | 36  |

| 3-19. Parameter Save Area and Local Variable Space                         | 37  |

| 3-20. Parameter Passing Example                                            | 45  |

| 3-21. Vector Parameter Passing Example                                     | 47  |

| 3-22. SPE Parameter Passing Example                                        | 48  |

| 3-23. Decimal Floating-Point Parameter Passing Example                     |     |

| 3-24. Profiling Example                                                    | 65  |

| 3-25. Absolute Load and Store Example                                      | 66  |

| 3-26. Small Model Position-Independent Load and Store                      | 67  |

| 3-27. Large Model Position-Independent Load and Store                      | 67  |

| 3-28. Direct Function Call                                                 | 68  |

| 3-29. Absolute Indirect Function Call                                      | 68  |

| 3-30. Small Model Position-Independent Indirect Function Call              | 69  |

| 3-31. Large Model Position-Independent Indirect Function Call              |     |

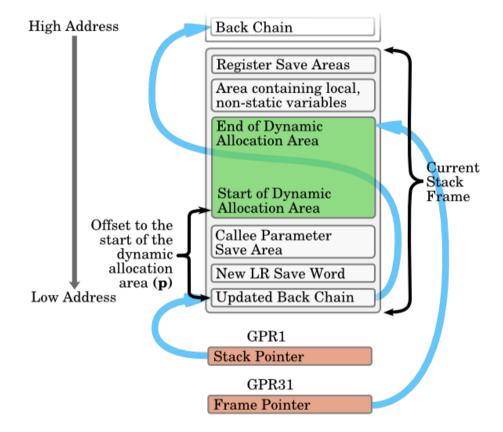

| 3-32. Before Dynamic Stack Allocation                                      | 71  |

| 3-33. Example code to allocate n bytes:                                    | 71  |

| 3-34. After Dynamic Stack Allocation                                       | 72  |

| 4-1. Section Ordering Under the BSS-PLT                                    | 77  |

| 4-2. Section Ordering Under the Secure-PLT                                 | 77  |

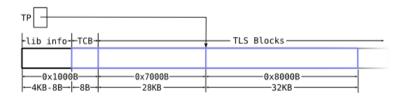

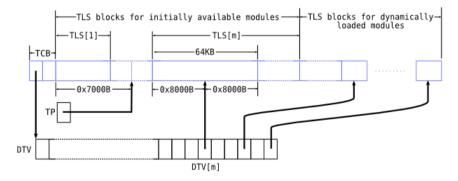

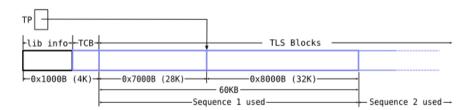

| 4-4. Thread Pointer Addressable Memory                                     | 93  |

| 4-5. TLS Block Diagram                                                     | 93  |

| 4-6. Local Exec TLS Model Sequences                                        |     |

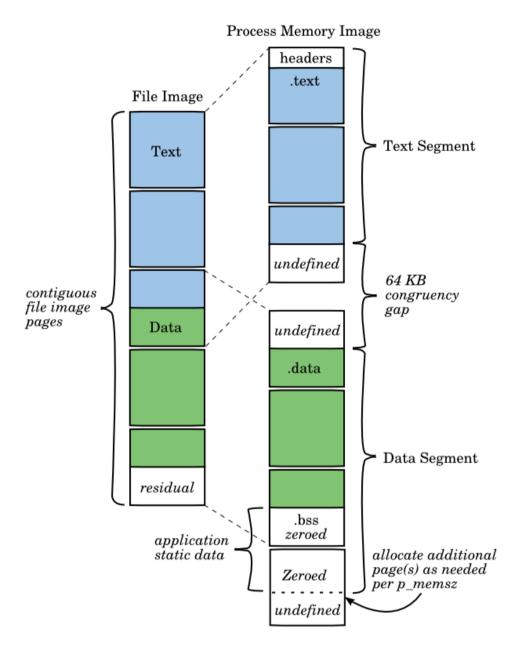

| 5-1. File Image to Process Memory Image Mapping                            |     |

| 5-2. Loading the Address of _GLOBAL_OFFSET_TABLE_ Under the Secure-PLT ABI | 109 |

| 5-3. Loading the Address of _GLOBAL_OFFSET_TABLE_ Under the BSS-PLT ABI    | 110 |

| 5-4. Example BSS-PLT .plt Section Implementation                           | 113 |

| 5-5. Example BSS-PLT Entries Post Resolution                               |     |

| A-1. Taxonomy                                                              | 129 |

# **List of Tables**

| 3-1. Bit and Byte Numbering in Halfwords                                                | 5  |

|-----------------------------------------------------------------------------------------|----|

| 3-2. Bit and Byte Numbering in Words                                                    | 5  |

| 3-3. Bit and Byte Numbering in Doublewords                                              | 5  |

| 3-4. Bit and Byte Numbering in Quadwords                                                | 5  |

| 3-5. Fundamental Types                                                                  | 7  |

| 3-6. SPE Types                                                                          | 8  |

| 3-7. Vector Types                                                                       | 8  |

| 3-8. Decimal Floating-Point Types                                                       | 9  |

| 3-9. IBM® AIX® Long Double 128 Type                                                     | 9  |

| 3-10. Long Double Is Double Type                                                        |    |

| 3-11. Bit-Field Types                                                                   | 14 |

| 3-12. Bit Numbering for 0x01020304                                                      | 15 |

| 3-13. Register Roles                                                                    | 20 |

| 3-14. TLS ABI Register Role for General-Purpose Register 2                              | 22 |

| 3-16. Register Roles for the _Complex float and _Complex double Types                   | 22 |

| 3-17. Register Roles for the _Complex Long Double Type                                  |    |

| 3-18. Secure-PLT Register Role for General-Purpose Register 30                          | 22 |

| 3-19. Floating-Point Register Roles for Binary Floating-Point Types                     | 23 |

| 3-20. Floating-Point Register Roles for Decimal Floating-Point Types                    | 23 |

| 3-21. Soft-Float General-Purpose Register Roles for Binary Floating-Point Types         |    |

| 3-22. Soft-Float General-Purpose Register Roles for Decimal Floating-Point Types        |    |

| 3-23. Vector Register Roles                                                             |    |

| 3-24. SPE Register Roles                                                                | 25 |

| 3-25. Parameter Passing Using IBM AIX 128-bit Long Double                               | 45 |

| 3-26. Parameter Passing Using IBM AIX 128-bit Long Double and Soft-Float                | 46 |

| 3-27. Parameter Passing Using long double is double                                     | 46 |

| 3-28. Parameter Passing Using long double is double and Soft-Float                      | 47 |

| 3-29. Parameter Passing of Vector Data Types                                            | 48 |

| 3-30. Parameter Passing of SPE Data Types                                               | 48 |

| 3-31. Decimal Floating-Point Parameter Passing on Classic Power Architecture (with FPU) | 49 |

| 3-32. Decimal Floating-Point Parameter Passing with Soft-Float (without FPU)            | 50 |

| 3-33. SPE Save And Restore Rules                                                        | 57 |

| 3-34. Register Mappings                                                                 | 73 |

| 4-1. e_flags Bit Masks                                                                  | 74 |

| 4-3. DWARF Additions Forev64_opaque Support                                             | 79 |

| 4-4. Typical Elf Note Section Format                                                    | 79 |

| 4-5. Object File a.o                                                                    | 80 |

| 4-6. Object File b.o                                                                    | 80 |

| 4-7. Merged Object File b.o                                                             | 80 |

| 4-8. APU Identifiers                                                                    | 81 |

| 4-9. Relocation Table                                                                   | 86 |

| 4-10. Relocation Table - Continued                                                      | 86 |

| 4-12. General Dynamic Initial Relocations                                               |    |

| 4-13. General Dynamic Outstanding Relocations                                           | 94 |

| 4-14. Local Dynamic Initial Relocations                                                 | 95 |

| 4-15. Local Dynamic Outstanding Relocations                                             | 95 |

| 4-16. Initial Exec Initial Relocations                                    | 95  |

|---------------------------------------------------------------------------|-----|

| 4-17. Initial Exec Outstanding Relocations                                | 95  |

| 4-18. Local Exec Initial Relocations (Sequence 1)                         | 96  |

| 4-19. Local Exec Initial Relocations (Sequence 2)                         | 96  |

| 4-20. General Dynamic to Initial Exec Initial Relocations                 | 97  |

| 4-21. General Dynamic to Initial Exec Outstanding Relocations             | 97  |

| 4-22. General Dynamic to Initial Exec Replacement Initial Relocations     | 97  |

| 4-23. General Dynamic to Initial Exec Replacement Outstanding Relocations | 97  |

| 4-24. General Dynamic to Local Exec Initial Relocations                   | 98  |

| 4-25. General Dynamic to Local Exec Outstanding Relocations               | 98  |

| 4-26. General Dynamic to Local Exec Replacement Initial Relocations       | 98  |

| 4-27. Local Dynamic To Local Exec Initial Relocations                     | 98  |

| 4-28. Local Dynamic To Local Exec Outstanding Relocations                 | 98  |

| 4-29. Local Dynamic To Local Exec Replacement Initial Relocations         | 99  |

| 4-30. Initial Exec to Local Exec Initial Relocations                      | 99  |

| 4-31. Initial Exec to Local Exec Outstanding Relocations                  | 99  |

| 4-32. Initial Exec to Local Exec Replacement Initial Relocations          | 99  |

| 4-33. Initial Exec to Local Exec X-form Initial Relocations               | 99  |

| 4-34. Initial Exec to Local Exec X-form Outstanding Relocations           | 100 |

| 4-35. Initial Exec to Local Exec X-form Replacement Initial Relocations   | 100 |

| 4-36. TLS Relocation Table                                                | 102 |

| 5-1. Program Header Example                                               | 105 |

| 5-2. Memory Segment Mappings                                              | 105 |

| C-1. APU Extensions and Corresponding Power ISA Categories                | 134 |

| C-2. APUs                                                                 | 134 |

# **Preface**

#### 1. How To Read This Document

Implementations of this *Power Architecture 32-bit Application Binary Interface Supplement* should indicate which *ABI software features* (see *Appendix A*) and Power ISA<sup>TM</sup> *categories* are implemented. When reading this document, the reader should reference those constraints and selectively read this text based upon them.

Appendix A provides a taxonomy of the information in this ABI document. The core of the ABI is common to all implementations and appears as nonconditional text, tables, and graphics.

Optional *ABI software feature* text or Power ISA *category* specific text is represented in the taxonomy as conditional attributes of the form **ATR-FOO** (where "FOO" is one of the attributes described in *Appendix A*). These attributes are used in the ABI text as element tags which aid in selective reading (and the generation) of this ABI document. These attributes describe the relationship of the optional elements of this document to a specific implementation.

This version of the *Power Architecture 32-bit Application Binary Interface Supplement* may take one of the following forms:

#### Linux & Embedded

The unified ABI document contains all text from all implementations of the ABI.

#### Linux

The technical conditions governing implementations of the Linux ABI are described by attribute conformance and inclusion rules in *Appendix B*, *Section B.1*. The attribute tags described in that part of the appendix are used to conditionally generate the Linux ABI variant of this document.

#### **Embedded**

The technical conditions governing implementations of the Embedded ABI are described by attribute conformance and inclusion rules in *Appendix B*, *Section B.2*. The attribute tags described in that part of the appendix are used to conditionally generate the Embedded ABI variant of this document.

Document elements representing *Categories* of the Power ISA are required for a software implementation based upon the implementation's conformance with either *Book III-S* or *Book III-E* of the Power ISA.

The following bounding box exemplifies a document element which corresponds to a *category* of the Power ISA.

#### ATR-SPE

This is an example of conditional text that applies to implementations that support the Signal Processing Engine (SPE) ABI, an optional *category* of the Power ISA.

This document also contains elements that correspond to optional *ABI software features* that may or may not be present in specific implementations. A prime differentiation would be software features used in embedded environments vs. those used in server environments, e.g., support for threading as defined by the Thread Local Storage ABI, support for the secure-PLT, or support for dynamic linking.

#### !ATR-PASS-COMPLEX-AS-STRUCT

This is an example of conditional text that applies to an implementation which **does not** support a specific software feature.

# 2. Section Numbering

The subsection numbering of the unified *Linux & Embedded* version of the *Power Architecture 32-bit Application Binary Interface Supplement* is sequential and does not skip digits between sibling subsections since it contains all of the text, tables, and graphics available.

The individual *Linux* and *Embedded* versions of the *Power Architecture 32-bit Application Binary Interface Supplement* contain a subset of the text, tables, and graphics available. The subsection numbers of these subset documents remain congruent with those of the *Linux & Embedded* version of the *Power Architecture 32-bit Application Binary Interface Supplement* (and with each other where they overlap) in order to prevent confusion during cross-reference and therefore subsection numbering can appear to skip digits between sibling subsections.

# **Chapter 1. Introduction**

The *Executable and Linkable Format* (ELF) defines a linking interface for executables and shared objects in two parts. The first part is the generic System V ABI. The second part is a processor-specific supplement.

This document is the processor-specific supplement for use with ELF on 32-bit Power Architecture processor systems. This is not a complete System V Application Binary Interface Supplement because it does not define any library interfaces.

Furthermore, this document establishes both big-endian and little-endian application binary interfaces (see Section 3.1.2.1). Processors in the 32-bit Power Architecture can execute in either big-endian or little-endian mode. Executables and executable generated data (in general) that subscribe to either byte ordering are not portable to a system running in the other mode.

Note: This ABI specification does not address little-endian byte ordering prior to Power ISA 2.03.

The Power Architecture 32-bit Application Binary Interface Supplement is not the same as the 64-bit PowerPC ELF ABI.

The *Power Architecture 32-bit Application Binary Interface Supplement* is intended to use the same structural layout now followed in practice by other processor specific ABIs.

# 1.1. Reference Documentation

The archetypal ELF ABI is described by the *System V ABI*. Supersessions and addenda that are 32-bit Power Architecture processor-specific are described in this document.

The following cited documents are complementary to this document and equally binding:

- Power Instruction Set Architecture Version 2.05, IBM, 2007. http://www.power.org/resources/reading/PowerISA\_V2.05.pdf

- DWARF Debugging Information Format Version 4, DWARF Debugging Information Format Workgroup, 2010. http://dwarfstd.org/Dwarf4Std.php

- ISO/IEC 9899:1999(E): Programming languages—C, as amended by ISO/IEC 9899:1999/Cor.1:2001(E), ISO/IEC 9899:1999/Cor.2:2004(E) and ISO/IEC 9899:1999/Cor.3:2007(E), http://www.open-std.org/JTC1/SC22/WG14/www/docs/n1256.pdf

### ATR-SPE

• SPEPIM: Signal Processing Engine Auxiliary Processing Unit Programming Interface Manual, Freescale Semiconductor, 2004.

http://www.freescale.com/files/32bit/doc/ref\_manual/SPEPIM.pdf?fsrch=1

#### ATR-VECTOR

ALTIVECPIM: AltiVec (TM) Technology Programming Interface Manual, Freescale Semiconductor, 1999. http://www.freescale.com/files/32bit/doc/ref\_manual/ALTIVECPIM.pdf

#### ATR-DFP

• ISO/IEC TR 24732:2009 - Programming languages, their environments and system software interfaces - Extension for the programming language C to support decimal floating-point arithmetic, ISO/IEC, January 05, 2009. Available from ISO.

### ATR-CXX

• *Itanium C++ ABI: Exception Handling. Rev 1.22*, CodeSourcery, 2001. http://www.codesourcery.com/public/cxx-abi/abi-eh.html

# ATR-TLS

• *ELF Handling for Thread-Local Storage. Version 0.20*, Ulrich Drepper, Red Hat Inc., December 21, 2005. http://people.redhat.com/drepper/tls.pdf

The following documents are of interest for their historical information but are not normative in any way.

- The [32-bit] PowerPC Processor Supplement, Sun Microsystems, 1995.

- The 32-bit AIX ABI.

- · The PowerOpen ABI.

# **Chapter 2. Software Installation**

# 2.1. Physical Distribution Media and Formats

This document does not specify any physical distribution media or formats. Any agreed-upon distribution media may be used.

# **Chapter 3. Low Level System Information**

# 3.1. Machine Interface

# 3.1.1. Processor Architecture

This Application Binary Interface (ABI) is not explicitly predicated on a minimum Power ISA version.

All nonoptional instructions that are defined by the Power Architecture® can be assumed to be implemented and work as specified. ABI conforming implementations must provide these instructions through software emulation if they are not provided by the processor.

Note: The exceptions to this rule are the *Fixed-point Load and Store Multiple* and *Fixed-point Move Assist* instructions which are not available in little-endian implementations because they would cause alignment exceptions.

Processors may support additional instructions beyond the published Instruction Set Architecture (ISA) and the Power Architecture optional ones, through *Auxiliary Processing Units* (APUs). This ABI provides a method for describing the additional instructions in section information (see *Section 4.4* and *Section 4.10*) but does not address these additional instructions directly and executing them may result in undefined behavior.

This ABI does not explicitly impose any performance constraints on systems.

# 3.1.2. Data Representation

# 3.1.2.1. Byte Ordering

The following standard data formats are recognized:

- 8-bit byte

- · 16-bit halfword

- 32-bit word

- 64-bit doubleword

- · 128-bit quadword

In big-endian byte ordering, the most significant byte is located in the lowest addressed byte position in memory (byte 0). This byte ordering is alternately referred to as *Most Significant Byte* (MSB) ordering.

In little-endian byte ordering, the least significant byte is located in the lowest addressed byte position in memory (byte 0). This byte ordering is alternately referred to as *Least Significant Byte* (LSB) ordering.

A specific processor implementation must state which type of byte ordering is to be used.

# ATR-SPE

Although it is possible on some processors to map some pages as little-endian, and other pages as big-endian in the same application, such an application does not conform to the ABI.

Table 3-1, Table 3-2, Table 3-3, and Table 3-4 show the conventions being assumed in big-endian and little-endian byte ordering at the bit and byte levels. These conventions are applied to integer and floating-point data types. Byte numbers are indicated in the upper corners, and bit numbers in the lower corners. Little-endian byte numbers are indicated on the right side; big-endian byte numbers are indicated on the left side.

Table 3-1. Bit and Byte Numbering in Halfwords

| 0 |     | 1 | 1 |     | 0  |

|---|-----|---|---|-----|----|

|   | msb |   |   | lsb |    |

| 0 |     | 7 | 8 |     | 15 |

Table 3-2. Bit and Byte Numbering in Words

| 0 |     | 3 | 1 | 2  | 2  | 1  | 3  | 0   |

|---|-----|---|---|----|----|----|----|-----|

|   | msb |   |   |    |    |    |    | lsb |

| 0 |     | 7 | 8 | 15 | 16 | 23 | 24 | 31  |

Table 3-3. Bit and Byte Numbering in Doublewords

| 0  | 7  | 1  | 6  | 2  | 5  | 3  | 4   |

|----|----|----|----|----|----|----|-----|

| ms | sb |    |    |    |    |    |     |

| 0  | 7  | 8  | 15 | 16 | 23 | 24 | 31  |

| 4  | 3  | 5  | 2  | 6  | 1  | 7  | 0   |

|    |    |    |    |    |    |    | lsb |

| 32 | 39 | 40 | 47 | 48 | 55 | 56 | 63  |

Table 3-4. Bit and Byte Numbering in Quadwords

| 0  | 15  | 1   | 14  | 2   | 13  | 3   | 12  |

|----|-----|-----|-----|-----|-----|-----|-----|

| m  | ısb |     |     |     |     |     |     |

| 0  | 7   | 8   | 15  | 16  | 23  | 24  | 31  |

| 4  | 11  | 5   | 10  | 6   | 9   | 7   | 8   |

|    |     |     |     |     |     |     |     |

| 32 | 39  | 40  | 47  | 48  | 55  | 56  | 63  |

| 8  | 7   | 9   | 6   | 10  | 5   | 11  | 4   |

|    |     |     |     |     |     |     |     |

| 64 | 71  | 72  | 79  | 80  | 87  | 88  | 95  |

| 12 | 3   | 13  | 2   | 14  | 1   | 15  | 0   |

|    |     |     |     |     |     | ls  | sb  |

| 96 | 103 | 104 | 111 | 112 | 119 | 120 | 127 |

Note: In the Power ISA, the figures are generally only shown in big-endian byte order. The bits in these data format specification are numbered from left to right (MSB to LSB).

#### ATR-SPE

Note: SPE documentation uses 64-bit numbering throughout, including for registers such as the CR that only contain 32 bits. This numbering can lead to some confusion. For example, although the CR bits are now numbered from 32 to 63, the same assembly instructions still work: crxor 6, 6, 6 operates on bit 32 + 6, that is, CR[38]. When discussing register contents, the bits are numbered 0: 63 for 64-bit registers and 32: 63 for 32-bit registers. When discussing memory contents, the bits are numbered naturally (for example, 0: 7 for bits within one byte and 0: 15 for bits within halfwords).

The bit numbering in the Power ISA is all 64-bit except for the following registers indicated in Power ISA section 1.4:

• Opcodes marking 0-31

#### ATR-VECTOR

• Vector registers and the VSCR (see Section 3.2.1).

#### ATR-CLASSIC-FLOAT

• As of Power ISA version 2.05 the FPSCR has been extended from 32-bits to 64-bits. The fields of the original 32-bit FPSCR are now held in bits 32-63 of the 64-bit FPSCR. The assembly instructions which operate upon the 64-bit FPSCR have either had a *W Instruction Field* added to select the operative word for the instruction, e.g., mtfsfi, or the instruction has been extended to operate upon

the entire 64-bit FPSCR, e.g., mffs. Reference to fields of the FPSCR, representing 1 or more bits, is done by field number with an indication of the operative word rather than by bit-number.

If the Power ISA version 2.05 DFP category is not needed by an implementation the FPSCR may continue to be referenced as a 32-bit register using the old forms of the instructions to support binary compatibility of ELF files built against an older Power ISA version. See *Section 3.2.1* for more information on the FPSCR.

# 3.1.2.2. Fundamental Types

The following tables map the data format specifications described in the Power ISA to ISO C scalar types. Each scalar type has a required alignment, which is indicated in the alignment column. Usage of these types in data structures must follow the alignment specified in the order encountered to ensure consistent mapping. When using variables individually, more strict alignment may be imposed if it has optimization benefits.

**Table 3-5. Fundamental Types**

| Туре        | ISO C Types        | sizeof | Alignment  | Description            |

|-------------|--------------------|--------|------------|------------------------|

| Boolean     | _Bool              | 1      | byte       | boolean                |

| Character   | char               | 1      | byte       | unsigned byte          |

|             | unsigned char      |        |            |                        |

|             | signed char        | 1      | byte       | signed byte            |

|             | short              | 2      | halfword   | signed halfword        |

|             | signed short       |        |            |                        |

|             | unsigned short     | 2      | halfword   | unsigned halfword      |

| Enumeration | signed enum        | 4      | word       | signed word            |

|             | unsigned enum      | 4      | word       | unsigned word          |

| Integral    | int                | 4      | word       | signed word            |

|             | signed int         |        |            |                        |

|             | long int           |        |            |                        |

|             | signed long        |        |            |                        |

|             | unsigned int       | 4      | word       | unsigned word          |

|             | unsigned long      |        |            |                        |

|             | long long          | 8      | doubleword | signed doubleword      |

|             | signed long long   |        |            |                        |

|             | unsigned long long | 8      | doubleword | unsigned doubleword    |

| Pointer     | any *              | 4      | word       | unsigned word          |

|             | any (*) ()         |        |            |                        |

| Floating    | float              | 4      | word       | single-precision float |

|             | double             | 8      | doubleword | double-precision float |

A NULL pointer has all bits zero.

Note: A boolean value is represented as a byte with value 0 or 1. If a byte with a value other than 0 or 1 is evaluated as a boolean value (for example, through the use of unions), the behavior is undefined.

Note: If an enumerated type contains a negative value, it is compatible with and has the same representation and alignment as int; otherwise it is compatible with and has the same representation and alignment as unsigned int.

Note: For each real floating-point type there is a corresponding complex type. This has the same alignment as the real type and twice the size; the representation is the real part followed by the imaginary part.

# ATR-SPE

Table 3-6. SPE Types

| Туре      | SPEPIM C Types | sizeof | Alignment  | Description                           |

|-----------|----------------|--------|------------|---------------------------------------|

| vector-64 | ev64_u16       | 8      | doubleword | vector of four unsigned halfwords     |

|           | ev64_s16       | 8      | doubleword | vector of four signed halfwords       |

|           | ev64_u32       | 8      | doubleword | vector of two unsigned words          |

|           | ev64_s32       | 8      | doubleword | vector of two signed words            |

|           | ev64_fs        | 8      | doubleword | vector of two single-precision floats |

|           | ev64_u64       | 8      | doubleword | 1 unsigned doubleword                 |

|           | ev64_s64       | 8      | doubleword | 1 signed doubleword                   |

|           | ev64_opaque    | 8      | doubleword | any of the above                      |

# ATR-VECTOR

**Table 3-7. Vector Types**

| Туре       | ALTIVECPIM C<br>Types | sizeof | Alignment | Description                            |

|------------|-----------------------|--------|-----------|----------------------------------------|

| vector-128 | vector unsigned char  | 16     | quadword  | vector of sixteen unsigned bytes       |

|            | vector signed char    | 16     | quadword  | vector of sixteen signed bytes         |

|            |                       |        | quadword  | vector of eight unsigned halfwords     |

|            | vector signed short   | 16     | quadword  | vector of eight signed<br>halfwords    |

|            | vector unsigned int   | 16     | quadword  | vector of four unsigned words          |

|            | vector signed int     | 16     | quadword  | vector of four signed words            |

|            | vector float          | 16     | quadword  | vector of four single-precision floats |

# ATR-SPE && ATR-VECTOR

Note: Availability of Vector data types is subject to conformance to a Power ISA category where the categories "Vector" and "SPE" are mutually exclusive.

# ATR-DFP

**Table 3-8. Decimal Floating-Point Types**

| Туре             | ISO TR 24732 C<br>Types | sizeof | Alignment  | Description                    |

|------------------|-------------------------|--------|------------|--------------------------------|

| Decimal Floating | _Decimal32              | 4      | word       | single-precision decimal float |

|                  | _Decimal64              | 8      | doubleword | double-precision decimal float |

|                  | _Decimal128             | 16     | quadword   | quad-precision decimal float   |

#### ATR-LONG-DOUBLE-IBM

# Table 3-9. IBM® AIX® Long Double 128 Type

| Type                | ISO C Types | sizeof | Alignment | Description                 |

|---------------------|-------------|--------|-----------|-----------------------------|

| IBM AIX long double | long double | 16     | quadword  | two double-precision floats |

#### ATR-LONG-DOUBLE-IS-DOUBLE

#### Table 3-10. Long Double Is Double Type

| Туре                  | ISO C Types | sizeof | Alignment  | Description            |

|-----------------------|-------------|--------|------------|------------------------|

| long double is double | long double | 8      | doubleword | double-precision float |

# ATR-LONG-DOUBLE-IBM && ATR-LONG-DOUBLE-IS-DOUBLE

Note: Availability of the long double data type is subject to conformance to a long double standard where the IBM AIX 128-bit Long Double format and the *Long Double is Double* format are mutually exclusive.

### ATR-LONG-DOUBLE-IS-DOUBLE || ATR-LONG-DOUBLE-IBM

This ABI provides the following choices for implementation of long double in compilers and systems:

#### ATR-LONG-DOUBLE-IS-DOUBLE

• Do not support any floating-point types with greater precision than double. In this case, long doubles and doubles have the same size and precision.

# ATR-LONG-DOUBLE-IBM

Provide support for the IBM AIX 128-bit Long Double format. In this format, double precision

numbers with different magnitudes that do not overlap, provide an effective precision of 106-bits.

The high-order double-precision value (the one that comes first in storage) must have the larger

magnitude. The high-order double-precision value must equal the sum of the two values, rounded

to nearest double.

- Extended precision provides the same range of double-precision (about 10<sup>-308</sup> to 10<sup>308</sup> but more precision (a variable amount, about 31 decimal digits or more).

- As the absolute value of the magnitude decreases (near the denormal range), the precision available in the low-order double also decreases.

- When the value represented is in the denormal range, this representation provides no more precision than 64-bit (double) floating-point.

- The actual number of bits of precision can vary. If the low-order part is much less then 1 unit of least precision (ULP) of the high-order part, significant bits (either all 0s or all 1s) are implied between the significands of high-order and low-order numbers. Some algorithms that rely on having a fixed number of bits in the significand can fail when using extended-precision.

This implementation differs from the IEEE 754 Standard in the following ways:

- The software support is restricted to round-to-nearest mode. Programs that use

extended-precision must ensure that this rounding mode is in effect when extended-precision

calculations are performed.

- Does not fully support the IEEE special numbers NaN and INF. These values are encoded in the high-order double value only. The low-order value is not significant, but the low-order value of an infinity must be positive or negative zero.

- Does not support the IEEE status flags for overflow, underflow, and other conditions. These flags have no meaning in this format.

# 3.1.2.3. Aggregates and Unions

The following are the rules for aggregates (structures and arrays) and unions that apply to their alignment and size.

- The entire aggregate or union must be aligned to its most strictly aligned member, which corresponds to the member with the largest alignment, including flexible array members.

- Each member is assigned the lowest available offset that meets the alignment requirements of the member. Depending on the previous member, internal padding can be required.

- The entire aggregate or union must have a size that is a multiple of its alignment. Depending on the last member, tail padding can be required.

For the following figures, the big-endian byte offsets are located in the upper left corners, and the little-endian byte offsets are located in the upper right corners.

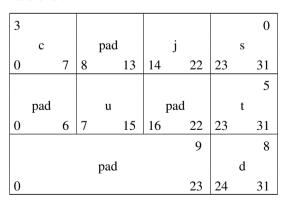

# Figure 3-1. Structure Smaller Than a Word

```

struct {

char c;

};

byte aligned, sizeof is 1

0 0

c

```

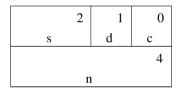

# Figure 3-2. Structure With No Padding

```

struct {

char c;

char d;

short s;

int n;

};

word-aligned, sizeof is 8

```

# little-endian

# big-endian

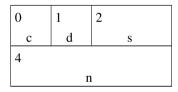

Figure 3-3. Structure With Internal Padding

```

struct {

char c;

short s;

};

halfword-aligned, sizeof is 4

little-endian

```

| 2 | 1   | 0 |

|---|-----|---|

| S | pad | c |

# big-endian

| 0 | 1   | 2 |

|---|-----|---|

| c | pad | s |

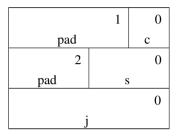

Figure 3-4. Structure With Internal and Tail Padding

```

struct {

char  c;

double d;

short s;

};

```

doubleword-aligned, sizeof is 24

# little-endian

big-endian

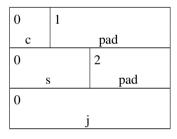

# Figure 3-5. Union Allocation

```

union {

char c;

short s;

int j;

};

word-aligned, sizeof is 4

```

#### little-endian

# big-endian

# 3.1.2.4. Bit-fields

Bit-fields can be present in definitions of C structures and unions. These bit-fields define whole objects within the structure or union where the number of bits in the bit-field is specified.

In the following table, a signed range goes from  $-(2^{(w-1)})$  to  $(2^{(w-1)})$  - 1 and an unsigned range goes from 0 to  $(2^w)$  - 1.

Table 3-11. Bit-Field Types

| Bit-field Type     | Width (w) |

|--------------------|-----------|

| _Bool              | 1         |

| signed char        | 1 to 8    |

| unsigned char      |           |

| signed short       | 1 to 16   |

| unsigned short     |           |

| signed int         | 1 to 32   |

| signed long        |           |

| unsigned int       |           |

| unsigned long      |           |

| enum               |           |

| signed long long   | 1 to 64   |

| unsigned long long |           |

Bit-fields can be signed or unsigned of type short, int, long, or long long. However, bit-fields shall have the same range for each corresponding type; for example, signed short must have the same range as unsigned short. All members of structures and unions must comply with the size and alignment rules including bit-fields. The following list of size and alignment rules additionally apply to bit-fields:

- The allocation of bit-fields is determined by the system endianess. For little-endian implementations the bit allocation is from the least significant (right) end to the most significant (left) end. The reverse is true for big-endian implementations; the bit allocation is from most significant (left) end to the least significant (right) end.

- A bit-field cannot cross its unit boundary; it must occupy the storage unit allocated for its declared type.

- If there is enough space within a storage unit, bit-fields must share the storage unit with other structure

members, including members that are not bit-fields. Clearly all the structure members occupy different

parts of the storage unit.

- The types of unnamed bit-fields have no effect on the alignment of a structure or union. However the offsets of an individual bit-field's member must comply with the alignment rules. An unnamed bit-field of zero width causes sufficient padding (possibly none) to be inserted for the next member, or the end of the structure if there are no more nonzero width members, to have an offset from the start of the structure that is a multiple of the size of the declared type of the zero-width member.

The byte offsets for structure and union members are shown in the examples below. The little-endian byte offsets are given in the upper right corners, and the big-endian byte offsets are given in the upper left corners. The bit numbers are given in the lower corners.

Table 3-12. Bit Numbering for 0x01020304

| 0 |    | 3 | 1 |    | 2  | 2  |    | 1  | 3  |    | 0  |

|---|----|---|---|----|----|----|----|----|----|----|----|

|   | 01 |   |   | 02 |    |    | 03 |    |    | 04 |    |

| 0 |    | 7 | 8 |    | 15 | 16 |    | 23 | 24 |    | 31 |

# Figure 3-6. Simple Bit-field Allocation

```

struct {

int j : 5;

int k : 6;

int m : 7;

};

word-aligned, sizeof is 4

```

#### little-endian

|   |     |    |    |    |   |    |    |   | 0  |

|---|-----|----|----|----|---|----|----|---|----|

|   | pad | m  |    |    | k |    |    | j |    |

| 0 | 13  | 14 | 20 | 21 |   | 26 | 27 |   | 31 |

# big-endian

| 0 |   |   |   |   |    |    |   |    |    |    |

|---|---|---|---|---|----|----|---|----|----|----|

|   | j |   |   | k |    |    | m |    | pa | ad |

| 0 |   | 4 | 5 |   | 10 | 11 |   | 17 | 18 | 31 |

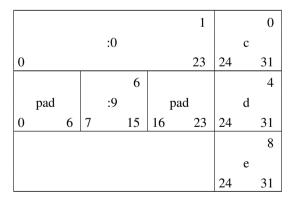

# Figure 3-7. Bit-Field Allocation With Boundary Alignment

```

struct {

short s : 9;

int j : 9;

char c;

short t : 9;

short u : 9;

char d;

};

```

word-aligned, sizeof is 12

#### little-endian

# big-endian

| 0 |   |   |   |     |    |    |     | 3  |     |

|---|---|---|---|-----|----|----|-----|----|-----|

|   | S |   |   | j   |    | ]  | pad |    | c   |

| 0 |   | 8 | 9 |     | 17 | 18 | 23  | 24 | 31  |

| 4 |   |   |   |     |    | 6  |     |    |     |

|   | t |   |   | pad |    |    | u   | ]  | pad |

| 0 |   | 8 | 9 |     | 15 | 16 | 24  | 25 | 31  |

| 8 |   |   | 9 |     |    |    |     |    |     |

|   | d |   |   |     |    | 1  | pad |    |     |

| 0 |   | 7 | 8 |     |    |    |     |    | 31  |

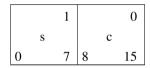

# Figure 3-8. Bit-Field Allocation With Storage Unit Sharing

```

struct {

char c;

short s : 8;

};

halfword-aligned, sizeof is 2

```

#### little-endian

# big-endian

Figure 3-9. Bit-Field Allocation In A Union

```

union {

char c;

short s : 8;

};

halfword-aligned, sizeof is 2

```

# little-endian

|   |     | 1 |   |   | 0  |

|---|-----|---|---|---|----|

|   | pad |   |   | c |    |

| 0 |     | 7 | 8 |   | 15 |

|   |     | 1 |   |   | 0  |

|   | pad |   |   | s |    |

| 0 |     | 7 | 8 |   | 15 |

# big-endian

| 0 |   |   | 1 |     |

|---|---|---|---|-----|

|   | c |   |   | pad |

| 0 |   | 7 | 8 | 15  |

| 0 |   |   | 1 |     |

|   | S |   |   | pad |

| 0 |   | 7 | 8 | 15  |

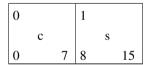

Figure 3-10. Bit-Field Allocation With Unnamed Bit-Fields

```

struct {

char c;

int : 0;

char d;

short : 9;

char e;

};

```

byte aligned, sizeof is 9

# little-endian

#### big-endian

| 0 |   |   | 1 |     |    |    |    |    |     |

|---|---|---|---|-----|----|----|----|----|-----|

|   | c |   |   |     |    | :0 |    |    |     |

| 0 |   | 7 | 8 |     |    |    |    |    | 31  |

| 4 |   |   |   |     | 6  |    |    |    |     |

|   | d |   |   | pad |    | :9 |    | ŗ  | oad |

| 0 |   | 7 | 8 | 15  | 16 |    | 24 | 25 | 31  |

| 8 |   |   |   |     |    |    |    |    |     |

|   | e |   |   |     |    |    |    |    |     |

| 0 |   | 7 |   |     |    |    |    |    |     |

Note: In *Figure 3-10* the alignment of the structure is not affected by the unnamed short and int fields. The named members are aligned relative to the start of the structure. However, it is possible that the alignment of the named members is not on optimum boundaries in memory. For instance, in an array of the structure in *Figure 3-10*, the *d* members will not all be on 4-byte (integer) boundaries.

# 3.2. Function Calling Sequence

The standard sequence for function calls is outlined in this section. The layout of the stack frame, the parameter passing convention, and the register usage is also detailed in this section. Standard library functions use these conventions, except as documented for the register save and restore functions.

The conventions given in this chapter are adhered to by C programs. Further information on the implementation of C is given in *Section 3.3*.

Note: While it is recommended that all functions use the standard calling sequence, the requirements of the standard calling sequence are only applicable to global functions. Different calling sequences and conventions can be employed by local functions which cannot be reached from other compilation units, if they comply with the stack back trace requirements.

#### ATR-LONG-DOUBLE-IS-DOUBLE

Note: If long double has the same representation as double, then all statements about how double values are passed to and returned from functions also apply to long double, and all statements about how \_Complex double values are passed to and returned from functions also apply to \_Complex long double.

# 3.2.1. Registers

Programs and compilers may freely use all registers except those reserved for system use. The system signal handlers are responsible for preserving the original values upon return to the original execution

path. Signals that can interrupt the original execution path are documented in (BA-OS) in the System V Interface Definition.

The tables in *Section 3.2.1.1* give an overview of the registers that are global during program execution. The tables use three terms to describe register *Preservation Rules*:

#### nonvolatile

A *caller* can expect that the contents of all registers marked *nonvolatile* are valid after control returns from a function call.

A *callee* shall save the contents of all registers marked *nonvolatile* prior to modification. The callee must restore the contents of all such registers before returning to its caller.

#### volatile

A *caller* cannot trust that the contents of registers marked *volatile* have been preserved across a function call.

A callee need not save the contents of registers marked volatile before modification.

#### limited-access

The contents of registers marked *limited-access* have special preservation rules. These registers have mutability restricted to certain bit-fields as defined by the Power ISA. The individual bits of these bit-fields are defined by this ABI to be *limited-access*.

Under normal conditions a *caller* can expect that these bits have been preserved across a function call. Under the special conditions, indicated in *Section 3.2.1.2*, a *caller shall expect* that these bit will have changed across function calls even if they have not.

A *callee* may only permanently modify these bits without preserving the state upon entrance to the function if the *callee* satisfies the special conditions indicated in *Section 3.2.1.2*; otherwise, these bits must be preserved before modification and restored before returning to the caller.

# 3.2.1.1. Register Roles

In the 32-bit Power Architecture, there are always 32 general-purpose registers, each 32 bits wide. Throughout this document the symbol r*N* is used, where *N* is a register number, to refer to general-purpose register *N*.

Table 3-13. Register Roles

| Register | Preservation Rules | Purpose                        |

|----------|--------------------|--------------------------------|

| r0       | volatile           | Optional in function linkage   |

| r1       | nonvolatile        | Stack frame pointer            |

| r2       | nonvolatile        | See the following table        |

| r3-r6    | volatile           | Parameter and return value     |

| r7-r10   | volatile           | Additional function parameters |

| r11-r12  | volatile           | Optional in function linkage   |

| r13      | nonvolatile        | Small data area pointer        |

| r14-r31  | nonvolatile        | Local variables                |

| LR       | volatile           | Link register                  |

| CTR      | volatile           | Loop count register            |

| XER      | volatile           | Fixed point exception register |

| CR0-CR1  | volatile           | Condition register fields      |

| CR2-CR4  | nonvolatile        | Condition register fields      |

| CR5-CR7  | volatile           | Condition register fields      |

|          |                    |                                |

# **Optional Function Linkage**

A function cannot depend on the values of those registers optional in the function linkage (r0, r11, and r12) because they may be altered by inter-library calls.

#### **Stack Frame Pointer**

The stack pointer always points to the lowest allocated valid stack frame. It must maintain quadword alignment and grow toward the lower addresses. The contents of the word at that address always points to the previously allocated stack frame. A called function is permitted to decrement it if required. See *Section 3.3.9* for additional information.

#### **Small Data Area Pointer**

Register r13 is the small data area pointer. Process start up code for executables that reference data in the small data area with 16-bit offset addressing relative to r13 must load the base of the small data area (the value of the dynamic linker-defined symbol \_SDA\_BASE\_) into r13. Shared objects shall not alter the value in r13. See *Section 4.7* for more details.

# Link Register

The link register contains the address a called function normally returns to. It is volatile across function calls.

# **Condition Register Fields**

In the condition register, the bit-fields CR2, CR3, and CR4 are nonvolatile and the value on entry must be restored on exit. The other bit-fields are volatile. The bit-field CR6 shall be set by the caller of a variable argument list function as described in *Section 3.2.4*.

# **ATR-TLS**

Table 3-14. TLS ABI Register Role for General-Purpose Register 2

| Register | <b>Preservation Rules</b> | Purpose        |

|----------|---------------------------|----------------|

| r2       | nonvolatile               | Thread pointer |

#### ATR-PASS-COMPLEX-IN-GPRS

Table 3-16. Register Roles for the \_Complex float and \_Complex double Types

| Register | <b>Preservation Rules</b> | Purpose                                     |

|----------|---------------------------|---------------------------------------------|

| r3-r10   | volatile                  | Used for _Complex float and _Complex double |

|          |                           | parameters and return values.               |

# ATR-PASS-COMPLEX-IN-GPRS && ATR-LONG-DOUBLE-IBM

Table 3-17. Register Roles for the \_Complex Long Double Type

| Register | Preservation Rules | Purpose                                                         |

|----------|--------------------|-----------------------------------------------------------------|

| r3-r10   | volatile           | Used for the _Complex long double parameters and return values. |

# ATR-SECURE-PLT

Under the Secure-PLT ABI, when using the *Position-Independent Code* (PIC) addressing model, register r30 is used (by convention between compiler & link editor) in nonleaf functions to hold the *Global Offset Table* (GOT) pointer. See *Section 5.2.5.2* for information on the Secure-PLT.

Table 3-18. Secure-PLT Register Role for General-Purpose Register 30

| Register | Preservation Rules | Purpose                                          |

|----------|--------------------|--------------------------------------------------|

| r30      | nonvolatile        | GOT pointer under the Secure-PLT with the        |

|          |                    | Position-Independent Code (PIC) addressing model |

#### ATR-CLASSIC-FLOAT

On Power Architecture processors that support Power ISA category *Floating-point*, there are always 32 floating-point registers, each 64 bits wide, and an associated special-purpose register to provide floating-point status and control. Throughout this document the symbol fN is used, where N is a register number, to refer to floating-point register N.

Table 3-19. Floating-Point Register Roles for Binary Floating-Point Types

| Register | <b>Preservation Rules</b> | Purpose                                                                                                                                                                                                                  |

|----------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f0       | volatile                  |                                                                                                                                                                                                                          |

| f1       | volatile                  | Used for <i>parameter passing</i> and <i>return values</i> of binary float types.                                                                                                                                        |

| f2-f8    | volatile                  | Used for parameter passing of binary float types.                                                                                                                                                                        |

| f9-f13   | volatile                  |                                                                                                                                                                                                                          |

| f14-f31  | nonvolatile               |                                                                                                                                                                                                                          |

| FPSCR    | limited-access            | Floating point status and control register limited-access bits. Preservation rules governing the limited-access bits for the bit-fields [VE], [OE], [UE], [ZE], [XE], and [RN] are presented in <i>Section 3.2.1.2</i> . |

#### ATR-CLASSIC-FLOAT && ATR-DFP

The ISA Decimal Floating-Point category extends the Power Architecture by adding a decimal floating-point unit. It uses the existing 64-bit floating-point registers and extends the FPSCR register to 64-bits, where it defines a decimal rounding-control field in the extended space.

Table 3-20. Floating-Point Register Roles for Decimal Floating-Point Types

| Register | Preservation Rules | Purpose                                                                                                                                                                                |

|----------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f0       | volatile           |                                                                                                                                                                                        |

| f1       | volatile           | Used for <i>parameter passing</i> and <i>return values</i> of <b>single-precision</b> and <b>double-precision</b> decimal floating-point types.                                        |

| f2-f8    | volatile           | Used for <i>parameter passing</i> and <i>return values</i> of <b>quad-precision</b> decimal floating-point types.                                                                      |

| f9-f13   | volatile           |                                                                                                                                                                                        |

| f14-f31  | nonvolatile        |                                                                                                                                                                                        |

| FPSCR    | limited-access     | Floating point status and control register limited-access bits. Preservation rules governing the limited-access bits for the bit-field [DRN] are presented in <i>Section 3.2.1.2</i> . |

# ATR-SOFT-FLOAT

Table 3-21. Soft-Float General-Purpose Register Roles for Binary Floating-Point Types

| Register | <b>Preservation Rules</b> | Purpose                                                                                                                                                                   |

|----------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| r3-r10   | volatile                  | Volatile parameter and return value registers for float, double, and long double binary floating-point types.                                                             |

|          |                           | If the parameters are within the first eight words of<br>the parameter list:                                                                                              |

|          |                           | • Float values occupy a single GPR.                                                                                                                                       |

|          |                           | • Double values occupy adjacent GPRs.                                                                                                                                     |

|          |                           | • Long double values occupy four adjacent GPRs.                                                                                                                           |

|          |                           | There are special rules governing how parameters that span multiple GPRs should be split between registers and the parameter save area outlined in <i>Section 3.2.3</i> . |

# ATR-SOFT-FLOAT && ATR-DFP

Table 3-22. Soft-Float General-Purpose Register Roles for Decimal Floating-Point Types

| Register | Preservation Rules | Purpose                                                                                                                                                                   |

|----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| r3-r10   | volatile           | Volatile parameter and return value registers for _Decimal32, _Decimal64, and _Decimal128 Decimal floating-point types                                                    |

|          |                    | If the parameters are within the first eight words of<br>the parameter list:                                                                                              |

|          |                    | • _Decimal32 values occupy a single GPR.                                                                                                                                  |

|          |                    | • _Decimal64 values occupy adjacent GPRs.                                                                                                                                 |

|          |                    | • _Decimal128 values occupy four adjacent GPRs.                                                                                                                           |

|          |                    | There are special rules governing how parameters that span multiple GPRs should be split between registers and the parameter save area outlined in <i>Section 3.2.3</i> . |

#### ATR-VECTOR

The ISA Vector category extends the Power Architecture and provides 32 vector registers, each 128 bits wide, a special-purpose register VRSAVE, and a special-purpose register VSCR. Throughout this document the symbol vN is used, where N is a register number, to refer to vector register N.

**Table 3-23. Vector Register Roles**

| Register | <b>Preservation Rules</b> | Purpose                                                                                                                                                          |

|----------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| v0-v1    | volatile                  |                                                                                                                                                                  |

| v2       | volatile                  | Used for parameter passing and return values                                                                                                                     |

| v3-v13   | volatile                  | Used for parameter passing                                                                                                                                       |

| v14-v19  | volatile                  |                                                                                                                                                                  |

| v20-v31  | nonvolatile               |                                                                                                                                                                  |

| VRSAVE   | nonvolatile               | 32-bit VR Save Register.                                                                                                                                         |

| VSCR     | limited-access            | 32-bit vector status and control register. Preservation rules governing the limited-access bits for the bit-field [NJ] are presented in <i>Section 3.2.1.2</i> . |

|          |                           |                                                                                                                                                                  |

#### ATR-SPE

The ISA Signal Processing Engine (SPE) category provides upper words for the 32 general-purpose registers, thus allowing them to be used in SPE APU operations to hold two 32-bit words. The Signal Processing Engine category also provides several special-purpose registers. The volatility of all 64-bit registers is the same for the upper and lower word. If only the lower word is modified by a function, only the lower word need be saved and restored.

**Table 3-24. SPE Register Roles**

| Register | <b>Preservation Rules</b> | Purpose                                                                                                                                                                                             |

|----------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPEFSCR  | limited-access            | Signal processing and embedded floating-point status and control register. Preservation rules governing the limited-access bits for the bit-fields [FINXE], [FINVE], [FDBZE], [FUNFE], [FOVFE], and |

|          |                           | [FRMC] are presented in <i>Section 3.2.1.2</i> .                                                                                                                                                    |

| ACC      | volatile                  | 64-bit SPE accumulator register.                                                                                                                                                                    |

# 3.2.1.2. Limited-Access Bits

The Power ISA identifies a number of registers which have mutability limited to the specific bit-fields indicated in the following list:

# ATR-CLASSIC-FLOAT FPSCR [VE] The Floating-Point Invalid Operation Exception Enable bit [VE] of the FPSCR register. ATR-CLASSIC-FLOAT FPSCR [OE] The Floating-Point Overflow Exception Enable bit [OE] of the FPSCR register. ATR-CLASSIC-FLOAT FPSCR [UE] The Floating-Point Underflow Exception Enable bit [UE] of the FPSCR register. ATR-CLASSIC-FLOAT FPSCR [ZE] The Floating-Point Zero Divide Exception Enable bit [ZE] of the FPSCR register. ATR-CLASSIC-FLOAT FPSCR [XE] The Floating-Point Inexact Exception Enable bit [XE] of the FPSCR register. ATR-CLASSIC-FLOAT FPSCR [RN] The Binary Floating-Point Rounding Control field [RN] of the FPSCR register.

# ATR-DFP FPSCR [DRN] The DFP Rounding Control field [DRN] of the 64-bit FPSCR register. ATR-VECTOR VSCR [NJ] The Vector Non-Java Mode field [NJ] of the VSCR register. ATR-SPE SPEFSCR [FINXE] The Embedded Floating-Point Round (Inexact) Exception Enable field [FINXE] of the SPEFSCR register. ATR-SPE SPEFSCR [FINVE] The Embedded Floating-Point Invalid Operation/Input Error Exception Enable field [FINVE] of the SPEFSCR register. ATR-SPE SPEFSCR [FDBZE] The Embedded Floating-Point Divide By Zero Exception Enable field [FDBZE] of the SPEFSCR register. **ATR-SPE**

#### SPEFSCR [FUNFE]

The *Embedded Floating-Point Underflow Exception Enable* field [FUNFE] of the SPEFSCR register.

#### ATR-SPE

#### SPEFSCR [FOVFE]

The Embedded Floating-Point Overflow Exception Enable field [FOVFE] of the SPEFSCR register.

#### ATR-SPE

#### SPEFSCR [FRMC]

The Embedded Floating-Point Rounding Mode Control field [FRMC] of the SPEFSCR register.

The bits composing these bit-fields are identified as *limited-access* because this ABI manages how they are to be modified and preserved across function calls.

*Limited-access* bits may be changed across function calls only if the called function has specific permission to do so as indicated by the following conditions.

A function without permission to change the *limited-access* bits across a function call shall save the value of the register before modifying the bits and restore it before returning to its calling function.

#### **Limited-Access Conditions**

- Standard library functions expressly defined to change the state of limited-access bits are not constrained by nonvolatile preservation rules, e.g., the fesetround() and feenableexcept() functions.

- All other standard library functions shall save the old value of these bits on entry, change the bits for their purpose, and restore the bits before returning.

- Where a standard library function such as qsort () calls functions provided by an application the following rules shall be observed:

- The limited-access bits on entry to the first call to such a callback must have the values they had on entry to the library function.

- The limited-access bits on entry to a subsequent call to such a callback must have the values they had on exit from the previous call to such a callback.

- The limited-access bits on exit from the library function must have the values they had on exit from the last call to such a callback.

- The compiler can directly generate code that saves and restores the limited-access bits.

- The values of the limited-access bits are unspecified on entry into a signal handler because a library or user function can temporarily modify the limited-access bits when the signal was taken.

• When set jmp() returns from a direct invocation, the limited-access bits must have the values they had on entry to setjmp; when it returns from a call to longjmp(), the limited-access bits must have the values they had on entry to longjmp().

#### ATR-CLASSIC-FLOAT

• C Library intrinsics, such as \_FPU\_SETCW(), may modify the limited-access bits of the FPSCR.

#### ATR-VECTOR

• The ALTIVEC PIM vec\_mtvscr() intrinsic may change the limited-access NJ bit.

#### ATR-SPE

• The following intrinsics defined by the SPE PIM may change the limited-access bits of the SPEFCSR register:

```

__ev_clr_spefscr_sovh() __ev_clr_spefscr_sov() __ev_clr_spefscr_finxs()

__ev_clr_spefscr_finvs() __ev_clr_spefscr_fdbzs() __ev_clr_spefscr_funfs()

__ev_clr_spefscr_fovfs() __ev_set_spefscr_frmc()

```

#### ATR-SOFT-FLOAT

• Any data stored internally by software floating-point code to describe rounding modes and enabled exceptions is subject to the same rules as limited-access register bits.

Note: The unwinder does not need to make specific allowances for limited-access bits.

# 3.2.2. The Stack Frame